# Application Note AN97072

#### Abstract

In this application note a pin by pin description of the new Bus-Controlled Autosync Deflection Controller TDA4853 and TDA4854 is given. One can find a summary of its specification and the internal pin specification, function description and drawings to illustrate the text. Also some layout and application proposals are given.

Purchase of Philips  $I^2C$  components conveys a license under the  $I^2C$  patent to use the components in the  $I^2C$  system, provided the system conforms to the  $I^2C$  specifications defined by Philips.

#### © Philips Electronics N.V. 1997

All rights are reserved. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner.

The information presented in this document does not form part of any quotation or contract, is believed to be accurate and reliable and may be changed without notice. No liability will be accepted by the publisher for any consequence of its use. Publication thereof does not convey nor imply any license under patent- or other industrial or intellectual property rights.

# **APPLICATION NOTE**

# AN97072

# Bus-Controlled Autosync Deflection Controller TDA4853/54

### Author(s):

#### P. Rombout / J. Moors

### Philips Semiconductors Systems Laboratory Eindhoven, The Netherlands

#### Keywords

Deflection Synchronisation Autosync Geometry EHT

Number of pages: 54 Date: 97-11-13

# Application Note AN97072

#### Summary

In this application note the new Bus-Controlled Autosync Deflection Controller TDA4853 and TDA4854 are described.

The TDA4853 is intended for 14" and 15" monitors. The TDA4854 is intended for 17" up to 21" monitors where also dynamic focus wave forms are required.

Basically the TDA4853 and TDA4854 are the successors of the successful TDA4858 and TDA4855. Besides the integration of the I<sup>2</sup>C bus with its internal DAC's also some extra functions are incorporated like extended geometry control, line parabola, size modulation etc.

The IC is described pin by pin.

For each pin a summary of its specification and the internal pin specification is given. Furthermore the purpose and functioning of this pin is described by some text, there where useful a drawing is given in illustrating the text.

For some pins an application proposal is given.

As performance greatly depends on a good layout, recommendations are given where necessary.

With the aid of this IC a monitor that combines high performance to low cost can be build. One example is the SLE promotion monitor CCM420 described in application note AN97032.

### CONTENTS

| 1. INTRODUCTION                                                                                                                         | 9  |

|-----------------------------------------------------------------------------------------------------------------------------------------|----|

| 2. PIN 1: HFLB                                                                                                                          |    |

| <ul><li>2.1 Characteristics / Internal configuration</li><li>2.2 Description</li><li>2.3 Application</li></ul>                          |    |

| 3. PIN 2/9: XRAY                                                                                                                        |    |

| <ul><li>3.1 Characteristics / Internal configuration</li><li>3.2 Description</li><li>3.3 Application</li></ul>                          |    |

| 4. PIN 3 / 4 / 5 / 6: BOP / BSENS / BIN / BDRV                                                                                          | 13 |

| <ul> <li>4.1 Characteristics / Internal configuration</li> <li>4.2 Description</li> <li>4.3 Application</li> <li>4.4 Lay-out</li> </ul> |    |

| 5. PIN 7/25: PGND/SGND                                                                                                                  |    |

| 5.1 Description<br>5.2 Application / Lay-out                                                                                            |    |

| 6. PIN 8: HDRV                                                                                                                          | 19 |

| 6.1 Characteristics / Internal configuration<br>6.2 Description<br>6.3 Application                                                      |    |

| 7. PIN 10: V <sub>cc</sub>                                                                                                              |    |

| <ul><li>7.1 Characteristics / Internal Configuration</li><li>7.2 Description</li><li>7.3 Application</li></ul>                          |    |

| 8. PIN 11: EWDRV                                                                                                                        |    |

| <ul><li>8.1 Characteristics / Internal configuration</li><li>8.2 Description</li><li>8.3 Application</li></ul>                          |    |

| 9. PIN 12 / 13: VOUT2 / VOUT1                                                                                                           |    |

| <ul> <li>9.1 Characteristics / Internal configuration</li> <li>9.2 Description</li> <li>9.3 Application</li> <li>9.4 Lay-out</li> </ul> |    |

| 10. PIN 14: VSYNC                                                                                                                       |    |

| 10.1 Characteristics / Internal configuration<br>10.2 Description<br>10.3 Application                                                   |    |

| 11. PIN 15: HSYNC                                                                                                                       |    |

| 11.1 Characteristics / Internal configuration                                                                                           |    |

# Application Note AN97072

| 11.2 Description<br>11.3 Application                                                                              |  |

|-------------------------------------------------------------------------------------------------------------------|--|

| 12. PIN 16: CLBL                                                                                                  |  |

| 12.1 Characteristics / Internal configuration<br>12.2 Description<br>12.3 Application                             |  |

| 13. PIN 17: HUNLOCK                                                                                               |  |

| <ul><li>13.1 Characteristics / Internal configuration</li><li>13.2 Description</li><li>13.3 Application</li></ul> |  |

| 14. PIN 18 / 19: SCL / SDA                                                                                        |  |

| <ul><li>14.1 Internal configuration</li><li>14.2 Description</li><li>14.3 Application</li></ul>                   |  |

| 15. PIN 20: ASCOR                                                                                                 |  |

| 15.1 Characteristics / Internal configuration<br>15.2 Description<br>15.3 Application                             |  |

| 16. PIN 21: VSMOD                                                                                                 |  |

| 16.1 Characteristics / Internal configuration<br>16.2 Description<br>16.3 Application<br>16.4 Lay-out             |  |

| 17. PIN 22 / 23 / 24: VAGC / VREF / VCAP                                                                          |  |

| 17.1 Characteristics / Internal configuration<br>17.2 Description<br>17.3 Application                             |  |

| 18. PIN 26 / 27 / 28 / 29: HPLL1 / HBUF / HREF / HCAP                                                             |  |

| <ul><li>18.1 Characteristics / Internal configuration</li><li>18.2 Description</li><li>18.3 Application</li></ul> |  |

| 19. PIN 30: PLL2                                                                                                  |  |

| 19.1 Characteristics / Internal configuration<br>19.2 Description<br>19.3 Application                             |  |

| 20. PIN 31: HSMOD                                                                                                 |  |

| 20.1 Characteristics / Internal configuration<br>20.2 Description<br>20.3 Application<br>20.4 Lay-out             |  |

| 21. PIN 32: FOCUS (TDA4854 ONLY)                                                                                  |  |

| 21.1 Characteristics                                                                                              |  |

# Bus-Controlled Autosync Deflection Controller Application Note AN97072 21.3 Application 51

|    | 21.3 Application                                                       | 51 |

|----|------------------------------------------------------------------------|----|

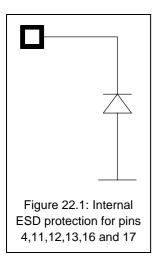

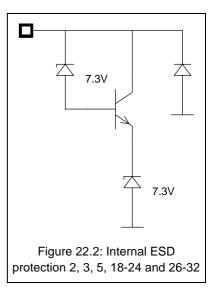

| 22 | . INTERNAL ESD PROTECTION                                              | 52 |

|    | 22.1 Pin 4, 11, 12, 13, 16 and 17<br>22.2 Pin 2, 3, 5, 18-24 and 26-32 |    |

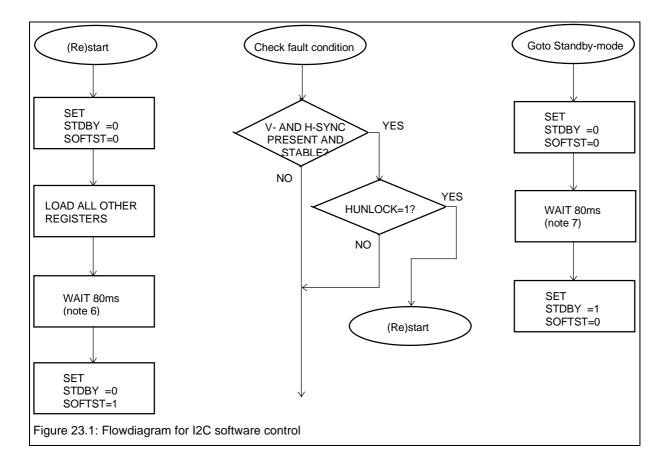

| 23 | . I2C SOFTWARE CONTROL                                                 | 53 |

| 24 | . REFERENCES                                                           | 54 |

#### 1. INTRODUCTION

The bus-controlled autosync monitor deflection controllers TDA4853/54 (bus-ASDC) are the successor types of autosync deflection controllers TDA4855/58 (ASDC). Main differences of the bus-ASDC, compared to the ASDC, are:

- I<sup>2</sup>C-bus driven extended geometry adjustments and functions, including stand-by mode;

- horizontal frequency range extended to 15-130kHz; vertical frequency range is 50-160Hz;

- combined horizontal/vertical focus section;

- moiré cancellation;

- TV/VCR mode.

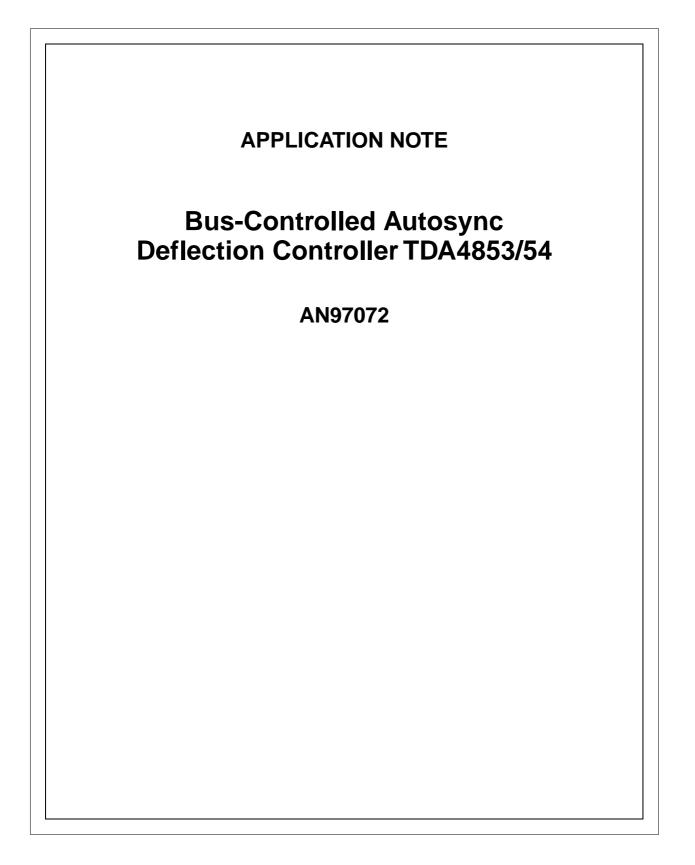

The IC pinning (32-pin shrink-DIL) of both TDA4853 and TDA4854 are shown in Figure 1.1 and Figure 1.2, with positive and negative current directions indicated.

All IC references are from its data sheet of 1997 April 25.

#### 2. PIN 1: HFLB

### 2.1 Characteristics / Internal configuration

| SYMBOL                                      | CONDITIONS                | MIN. | TYP.  | MAX. | UNIT |

|---------------------------------------------|---------------------------|------|-------|------|------|

| V <sub>HFLB</sub> positive clamping level   | I <sub>HFLB</sub> = 5 mA  | -    | 5.5   | -    | V    |

| V <sub>HFLB</sub> negative clamping level   | I <sub>HFLB</sub> = -1 mA | -    | -0.75 | -    | V    |

| I <sub>HFLB</sub> positive clamping current |                           | -    | -     | 6    | mA   |

| I <sub>HFLB</sub> negative clamping current |                           | -    | -     | -2   | mA   |

| $V_{\rm HFLB}$ slicing level                | I <sub>HFLB</sub> = 5 mA  | -    | 2.8   | -    | V    |

#### 2.2 Description

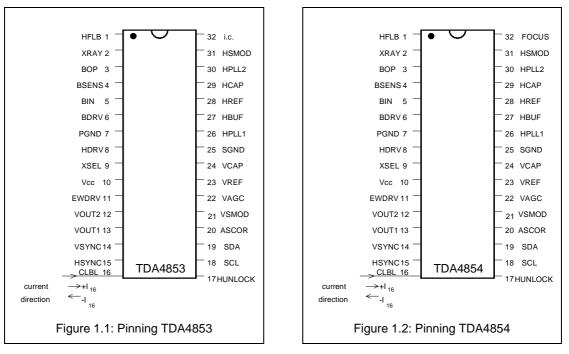

The horizontal flyback input HFLB is used for the PLL2 phase detector, that compares the flyback pulse to the horizontal oscillator's saw-tooth voltage. The PLL2 detector compensates for the delay in the external deflection circuit by adjusting the phase of the horizontal drive output pulse (HDRV).

### 2.3 Application

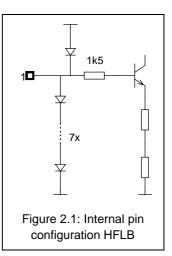

HFLB is connected to a converted horizontal flyback pulse of about 15 V<sub>pp</sub>. Figure 2.2 shows the application of HFLB. The conversion of about 1100 V<sub>pp</sub> to 15 V<sub>pp</sub> is done by the fraction C1\C2. Resistor R1 limits the current and C3 is applied for high frequency filtering.

#### 3. PIN 2/9: XRAY

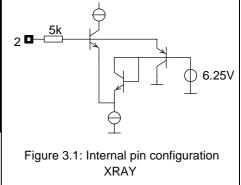

#### 3.1 Characteristics / Internal configuration

| SYMBOL                                             | CONDITIONS                     | MIN. | TYP. | MAX. | UNIT |

|----------------------------------------------------|--------------------------------|------|------|------|------|

| V <sub>XRAY</sub> slicing level                    |                                | 6.22 | 6.39 | 6.56 | V    |

| t <sub>WXRAY)</sub> minimum trigger<br>pulse width |                                | 20   | -    | -    | μs   |

| R <sub>in(XRAY)</sub>                              | $V_{XRAY}$ < 6.38 V + $V_{BE}$ | 500  | -    | -    | kΩ   |

|                                                    | $V_{XRAY}$ > 6.38 V + $V_{BE}$ | -    | 5    | -    | kΩ   |

#### 3.2 Description

The XRAY protection input consists of a voltage detector with a precise threshold. If this threshold is exceeded for a certain time, control bit SOFTST is reset and the IC goes into protection mode. In this mode, the following states are defined:

- 1. HUNLOCK (pin 17) is floating;

- 2. Capacitor at HPLL2 (pin 30) is discharged;

- 3. HDRV (pin 8) is floating;

- 4. BDRV (pin 6) is floating;

- 5. VOUT1 and VOUT2 (pin 12 and 13) are floating;

- 6. CLBL (pin 16) provides continuous blanking.

The possibility to reset the internal XRAY latch via I2C bus depends on the application of pin 9:

a) Pin 9 open or grounded : Same function as

TDA4854 V1D (XRAY is reset via control bit SOFTST)

- b) with an external resistor from Pin 9 to Pin 10 (VCC):

- No XRAY reset via I2C bus possible

- State of internal XRAY latch is kept for Vcc > 4V

- XRAY latch is reset for Vcc < 1V

|                        | X-ray latch triggered |                   |

|------------------------|-----------------------|-------------------|

| V <sub>XRAY</sub>      |                       |                   |

| VHUNLOCK               |                       |                   |

| BDRV duty cycle        | <u> </u>              | floating          |

| HDRV duty cycle        |                       | floating          |

| Vout1,Vout2            |                       | floating          |

|                        | ←approx. 35 ms→       |                   |

| Figure 3.2: Activation | on of soft-down sequ  | ence via pin XRAY |

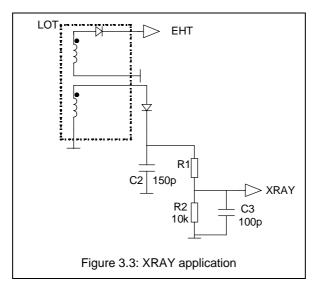

### 3.3 Application

For XRAY protection, the EHT must be limited to the tube's specification. The flyback pulse from the LOT can be rectified and fed to XRAY via a divider, because it is proportional to the EHT. This principle is shown in Figure 3.3. The value for R1 should be dimensioned in such a way that the divider voltage crosses the XRAY threshold if the EHT has reached the specified upper limit. This upper EHT limit is usually 30 kV.

If the XRAY input is not used, it should be grounded.

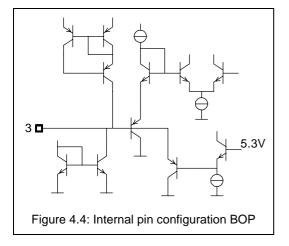

# 4. PIN 3 / 4 / 5 / 6: BOP / BSENS / BIN / BDRV

# 4.1 Characteristics / Internal configuration

| SYMBOL                                                     | CONDITIONS                                                      | MIN. | TYP.  | MAX. | UNIT |                                                                                                                                                            |

|------------------------------------------------------------|-----------------------------------------------------------------|------|-------|------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Transconductance a                                         | amplifier BOP and BIN                                           | •    |       |      |      |                                                                                                                                                            |

| V <sub>BIN</sub>                                           |                                                                 | 0    | -     | 5.25 | V    | $\square \square $ |

| I <sub>BIN(max)</sub>                                      |                                                                 | -    | -     | ± 1  | μΑ   |                                                                                                                                                            |

| V <sub>ref</sub> internal non-<br>inverting input OTA      |                                                                 | 2.37 | 2.5   | 2.58 | V    |                                                                                                                                                            |

| V <sub>BOP</sub>                                           | comparator inv. input voltage range                             | 0    | -     | 5    | V    |                                                                                                                                                            |

| V <sub>BOP(min)</sub>                                      |                                                                 | -    | 0.4   | -    | V    |                                                                                                                                                            |

| V <sub>BOP(max)</sub>                                      | I <sub>BOP</sub> < 1 mA (internal prot. circuit clamp level)    | 5.0  | 5.3   | 5.6  | V    | Figure 4.1: Internal pin configuration BSENS                                                                                                               |

| I <sub>BOP(max)</sub>                                      |                                                                 | -    | ± 500 | -    | μA   |                                                                                                                                                            |

| 9 <sub>ota</sub>                                           | first pole at 5 MHz (second pole if OTA operates as integrator) | 30   | 50    | 70   | mS   |                                                                                                                                                            |

| $G_{open, DC}\left(V_{BOP}\!\!\setminus\!\!V_{BIN}\right)$ | $C_{BOP} = 4.7 \text{ nF}$ , no resistive load                  | -    | 86    | -    | dB   |                                                                                                                                                            |

| C <sub>BOP(min)</sub>                                      |                                                                 | 4.7  | -     | -    | nF   |                                                                                                                                                            |

| Voltage Comparator                                         | r BSENS                                                         |      |       |      | •    |                                                                                                                                                            |

| V <sub>BSENS</sub>                                         | comparator noninv. input voltage range and OTA output           | 0    | -     | 5    | V    | ⊥<br>Figure 4.2: Internal pin                                                                                                                              |

| V <sub>BSENS, stop</sub>                                   | capacitive load; $I_{BSENS} = 0.5$ mA.                          | 0.85 | 1.0   | 1.15 | V    | configuration BIN                                                                                                                                          |

| IBSENS, discharge                                          | V <sub>BSENS</sub> > 2.5 V                                      | 4.5  | 6.0   | 7.5  | mA   |                                                                                                                                                            |

| V <sub>BSENS, restart</sub>                                | fault condition                                                 | 1.2  | 1.3   | 1.4  | V    |                                                                                                                                                            |

| C <sub>BSENS(min)</sub>                                    |                                                                 | 2    | -     | -    | nF   |                                                                                                                                                            |

| BSENS(max)                                                 | discharge disabled (leakage current)                            | -    | -     | -2   | μΑ   |                                                                                                                                                            |

| Open Collector Out                                         | put Stage BDRV                                                  | •    | •     | •    |      |                                                                                                                                                            |

| I <sub>BDRV(max)</sub>                                     |                                                                 | 20   | -     | -    | mA   | Figure 4.3: Internal                                                                                                                                       |

| I <sub>BDRV, leak</sub>                                    | V <sub>BDRV</sub> = 16 V                                        | -    | -     | 3    | μΑ   | pin configuration<br>BDRV                                                                                                                                  |

| V <sub>BDRV, sat</sub>                                     | I <sub>BDRV</sub> < 20 mA                                       | -    | -     | 300  | mV   |                                                                                                                                                            |

| t <sub>off(min)</sub>                                      |                                                                 | -    | 250   | -    | ns   |                                                                                                                                                            |

| t <sub>d, BDRV</sub>                                       | V <sub>HDRV</sub> = 3 V; V <sub>BDRV</sub> = 3 V.               | -    | 500   | -    | ns   |                                                                                                                                                            |

# Application Note AN97072

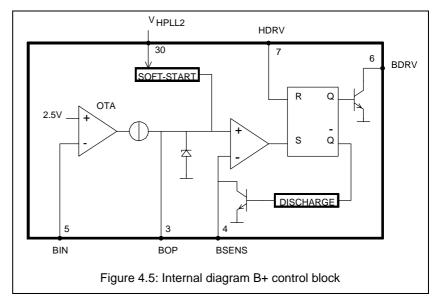

### 4.2 Description

The B+ function block is built up as shown in Figure 4.5. BIN is fed to the inverting input of the OTA. The OTA output is connected to BOP. An internal clamp diode (5.3V) prevents BOP from too high voltages. Also, the output is compared to BSENS. The output of this comparator sets the flipflop that drives the open collector stage for BDRV. The flip-flop is reset by HDRV. The flip-flop is an edgetriggered device. The recommended value for the load resistor for BDRV is  $470\Omega$ .

### 4.3 Application

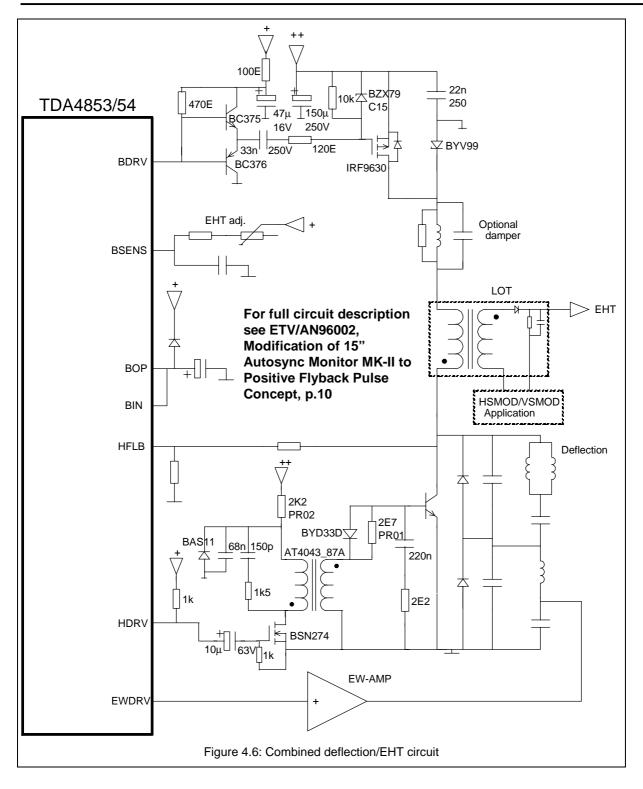

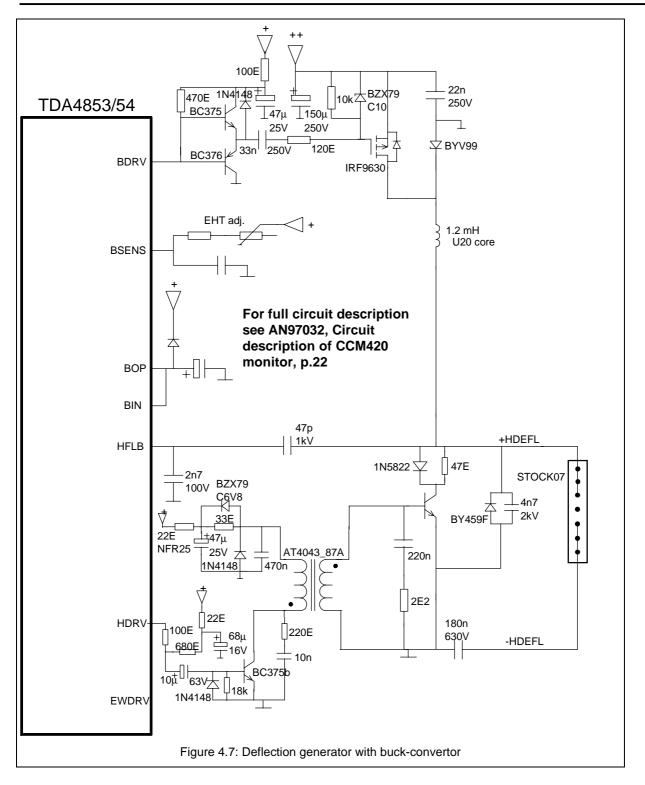

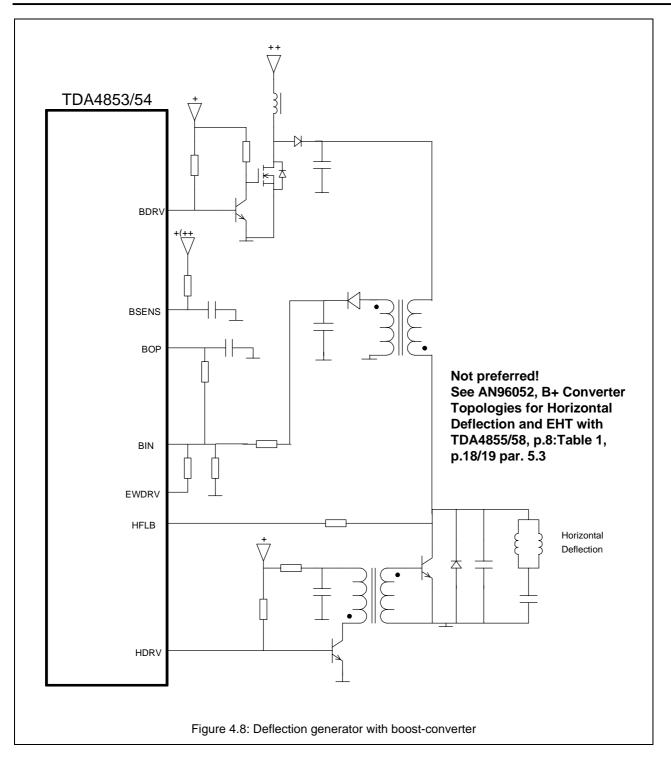

The B+ function block can be used for many different deflection topologies. Two common applications are the combined deflection/EHT circuit for 14"/15" monitors (Figure 4.6) and the deflection generator with buck-converter (Figure 4.7). Another application is the deflection generator with boost-convertor, however this application is not tested (Figure 4.8). For a more detailed description and other applications, see Application Note AN96052: 'B+ Converter Topologies for Horizontal Deflection and EHT Generators' (see ref. 6).

#### 4.4 Lay-out

The PCB track that is connected to BIN should be as short as possible in order to limit EMI. This means that, if a resistor is connected to BIN, this resistor should be as close to pin BIN as possible.

# Application Note AN97072

#### 5. PIN 7/25: PGND/SGND

#### 5.1 Description

Power ground PGND is connected to the substrate and signal ground SGND must be connected externally to PGND.

### 5.2 Application / Lay-out

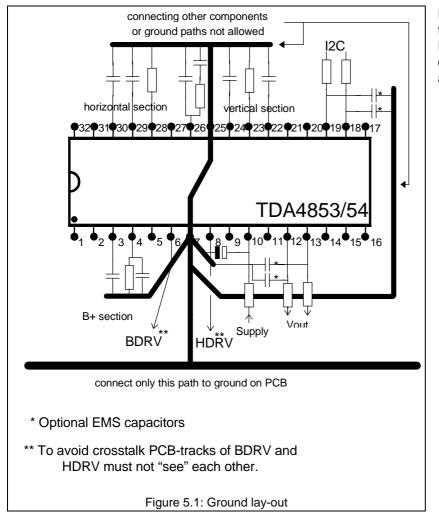

For optimum performance, ground tracks should be routed as shown in Figure 5.1. Only one connection to other ground tracks of the PCB is allowed.

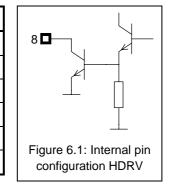

#### 6. PIN 8: HDRV

### 6.1 Characteristics / Internal configuration

| SYMBOL                            | CONDITIONS                                            | MIN. | TYP. | MAX. | UNIT |

|-----------------------------------|-------------------------------------------------------|------|------|------|------|

| V <sub>HDRV, sat</sub>            | I <sub>HDRV</sub> = 20 mA                             | -    | -    | 0.3  | V    |

|                                   | I <sub>HDRV</sub> = 60 mA                             | -    | -    | 0.8  | V    |

| I <sub>HDRV,leak</sub>            | V <sub>HDRV</sub> = 16 V                              | -    | -    | 10   | μΑ   |

| $t_{\rm HDRV, off}$ / $t_{\rm H}$ | I <sub>HDRV</sub> = 20 mA, f <sub>H</sub> = 31.45 kHz | 42   | 45   | 48   | %    |

|                                   | $I_{HDRV} = 20 \text{ mA}, f_{H} = 58 \text{ kHz}$    | 45.5 | 48.5 | 51.5 | %    |

|                                   | $I_{HDRV}$ = 20 mA, f <sub>H</sub> = 110 kHz          | 49   | 52   | 55   | %    |

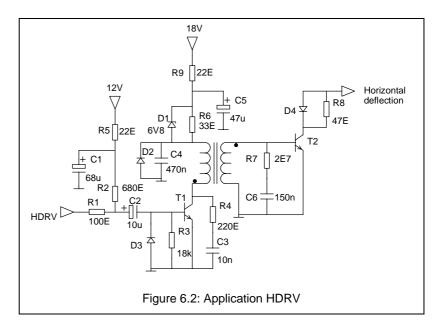

#### 6.2 Description

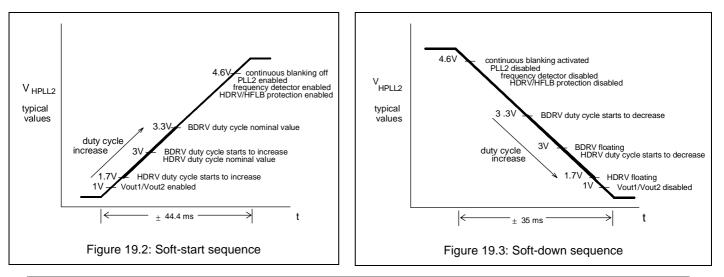

The horizontal drive pulse (HDRV) is an open collector output that can directly drive the driver transistor. Optimised drive conditions are achieved over the whole frequency range by the slightly frequency-dependent duty cycle. The output duty cycle will decrease if the supply voltage  $V_{HPLL2}$  drops below 3 V and passes into a floating state if  $V_{HPLL2}$  decreases to 1.7 V.

#### 6.3 Application

A typical 17" application is shown in Figure 6.2. For a more detailed description of this horizontal drive application, see application note AN96091: 'Low Power and Low Cost Horizontal Drive Circuits with U15 Core' (see ref. 5).

### 7. PIN 10: V<sub>cc</sub>

### 7.1 Characteristics / Internal Configuration

| SYMBOL                                                                    | CONDITIONS                                                                      | MIN. | TYP. | MAX. | UNIT |                             |

|---------------------------------------------------------------------------|---------------------------------------------------------------------------------|------|------|------|------|-----------------------------|

| V <sub>cc</sub> normal mode                                               |                                                                                 | 9.2  | -    | 16   | V    |                             |

| V <sub>cc</sub> activation continuous blanking mode                       | V <sub>cc</sub> decreasing from 12 V                                            | 8.2  | 8.6  | 9.0  | V    |                             |

| V <sub>cc(min)</sub> continuous<br>blanking mode                          | $V_{cc}$ decreasing from 12 V                                                   | 2.5  | 3.5  | 4.0  | V    | Figure 7.1:<br>Internal pin |

| V <sub>cc</sub> disable HDRV, BDRV,<br>VOUT1/2 and HUNLOCK,<br>SOFTST set | V <sub>cc</sub> decreasing from 8.2 V typ.<br>via SOFTST                        | 7.7  | 8.1  | 8.5  | V    | configuration Vcc           |

| $V_{cc}$ enable HDRV, BDRV, VOUT1/2 and HUNLOCK                           | V <sub>cc</sub> increasing from 8 V typ. via<br>SOFTST                          | 7.9  | 8.3  | 8.7  | V    |                             |

| I <sub>Vcc</sub>                                                          |                                                                                 | -    | 60   | -    | mA   |                             |

| I <sub>Vcc, stand-by</sub>                                                | SOFTST is reset;<br>V <sub>PLL2</sub> < 1 V;<br>3.5 V < V <sub>CC</sub> < 16 V. | -    | 9    | -    | mA   |                             |

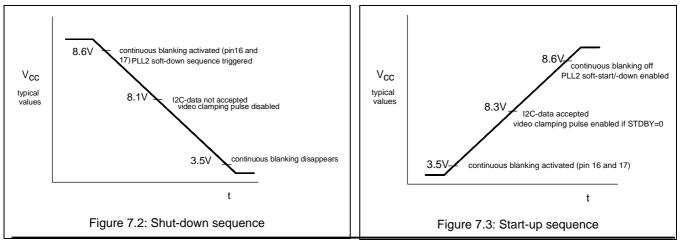

#### 7.2 Description

The internal voltage stabilizer provides all internal references with a stabilised voltage. If  $V_{cc}$  drops below (typically) 8.3V or no I<sup>2</sup>C-data has been received after power-up, internal soft-start and protection functions disable HDRV, BDRV, VOUT1/VOUT2 and HUNLOCK. Also, the internal I<sup>2</sup>C-bus will not generate an acknowledge and SOFTST is reset, forcing the IC into stand-by mode. Figure 7.2 and Figure 7.3 show this shut-down and start-up sequence.

# Application Note AN97072

If, during normal operation,  $V_{cc}$  drops below (typically) 8.1 V, protection mode is activated and HUNLOCK passes into protection status (floating). This mode protects the deflection stages and tube during start-up, shut-down and fault conditions. The table at the right shows the measures how the normal mode can be entered after protection has occured. If the soft-start procedure is activated via I<sup>2</sup>C-bus, protection actions will be performed in a well-defined sequence. This is the same sequence as pulling HPLL2 to ground, see HPLL2 (pin 30).

| EVENT                                      | ACTION                                                                                |

|--------------------------------------------|---------------------------------------------------------------------------------------|

| Low supply voltage                         | increase supply voltage;<br>reload registers;<br>soft start via I <sup>2</sup> C-bus. |

| Power dip (V <sub>cc</sub> < 8.1V)         | reload registers;<br>soft start via I <sup>2</sup> C-bus.                             |

| XRAY (pin 2) triggered                     | reload registers;<br>soft start via I <sup>2</sup> C-bus.                             |

| HPLL2 (pin 30) externally pulled to ground | release HPLL2 (pin 30)                                                                |

If protection mode is active, several pins are forced into a defined state:

- 1. HUNLOCK (pin 17) is floating;

- 2. Capacitor at HPLL2 (pin 30) is discharged;

- 3. HDRV (pin 8) is floating;

- 4. BDRV (pin 6) is floating;

- 5. VOUT1 and VOUT2 (pin 12 and 13) are floating;

- 6. CLBL (pin 16) provides continuous blanking.

Protection mode can be changed into normal operation by setting bit SOFTST=1.

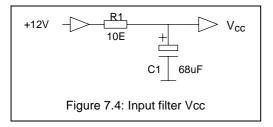

### 7.3 Application

The supply pin is connected by a series resistor and must be decoupled by an electrolytic capacitor of about 68uF, as close as possible to the pin itself (see Figure 7.4).

## 8. PIN 11: EWDRV

# 8.1 Characteristics / Internal configuration

| SYMBOL                                                                      | CONDITIONS                                                                                                                                  | MIN. | TYP.  | MAX. | UNIT |                                                    |

|-----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------|------|----------------------------------------------------|

| V <sub>EWDRV,const</sub><br>bottom output                                   | register HPIN = $0_{DEC}$<br>register HCOR = $04_{DEC}$                                                                                     | 1.05 | 1.2   | 1.35 | V    |                                                    |

| Internally<br>stabilised                                                    | register HTRAP = $08_{DEC}$<br>register HSIZE = $255_{DEC}$                                                                                 |      |       |      |      | 108E                                               |

| V <sub>EWDRV(max)</sub><br>maximum output                                   | Clipping if control bit VOVSCN=1 and VPOS is<br>extreme. Corner clipping if vertical saw-tooth > 110% of<br>nominal value                   | 7.0  | -     | -    | V    | <sub>11</sub> <b>D</b>  <br>   108E                |

| V <sub>ewdrv</sub><br>parabola                                              | Frequency tracking from 15 to 80 kHz<br>control bit FMULT=1, $f_H = 31.45$ kHz                                                              | -    | 0.72  | -    | V    |                                                    |

|                                                                             | Frequency tracking from 15 to 80 kHz<br>control bit FMULT=1, $f_{H} = 70$ kHz                                                               | -    | 1.42  | -    | V    |                                                    |

|                                                                             | Frequency tracking disabled<br>control bit FMULT=0                                                                                          | -    | 1.42  | -    | V    | Figure 8.1: Internal<br>pin configuration<br>EWDRV |

| δV <sub>ewdRV</sub><br>parabola                                             | Linearity error with frequency tracking (FMULT=1)                                                                                           | -    | -     | 8    | %    |                                                    |

| values for<br>$V_{HPIN}$ , $V_{HCOR}$<br>$V_{HTRAP}$ , $V_{HSIZE}$<br>below | Nominal vertical settings (unless specified otherwise):<br>VSIZE=127 <sub>DEC</sub> and VOVSCN=0, VSMOD=0µA, VPC=1,<br>VSC=1, VLC=1, HPC=1. |      |       |      |      |                                                    |

| V <sub>HPIN</sub>                                                           | Register HPIN=0 <sub>DEC</sub>                                                                                                              | -    | 0.04  | -    | V    |                                                    |

|                                                                             | Register HPIN=63 <sub>DEC</sub>                                                                                                             | -    | 1.42  | -    | V    |                                                    |

| V <sub>hcor</sub>                                                           | Register HCOR=0 <sub>DEC</sub><br>control bit VSC=0                                                                                         | -    | 0.08  | -    | V    |                                                    |

|                                                                             | Register HCOR=31 <sub>DEC</sub><br>control bit VSC=0                                                                                        | -    | -0.64 | -    | V    |                                                    |

# Application Note AN97072

|                    | Register HCOR=X <sub>DEC</sub>    | - | 0     | - | V |

|--------------------|-----------------------------------|---|-------|---|---|

|                    | control bit VSC=1                 |   |       |   |   |

| V <sub>htrap</sub> | Register HTRAP=0 <sub>DEC</sub>   | - | 0.33  | - | V |

|                    | Control bit VPC=0                 |   |       |   |   |

|                    | Register HTRAP=15 <sub>DEC</sub>  | - | -0.33 | - | V |

|                    | Control bit VPC=0                 |   |       |   |   |

|                    | Register HTRAP=X <sub>DEC</sub>   | - | 0     | - | V |

|                    | Control bit VPC=1                 |   |       |   |   |

| V <sub>HSIZE</sub> | Register HSIZE=0 <sub>DEC</sub>   | - | 3.6   | - | V |

|                    | Register HSIZE=255 <sub>DEC</sub> | - | 0.13  | - | V |

| V <sub>HSMOD</sub> | Ι <sub>HSMOD</sub> = -120 μΑ      | - | 0.69  | - | V |

|                    | $I_{HSMOD} = 0 \ \mu A$           | - | 0.02  | - | V |

### 8.2 Description

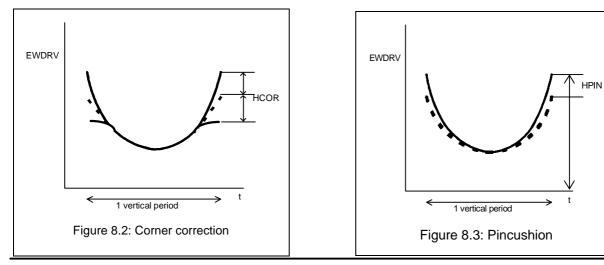

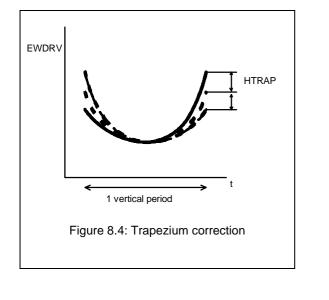

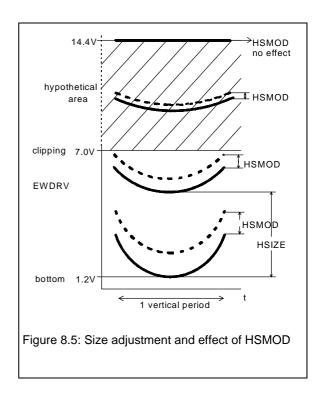

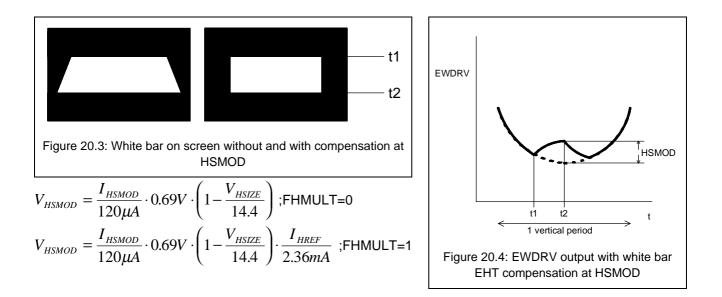

The parabola wave-form of the EW-drive output is controlled by I2C-registers horizontal pincushion (HPIN), horizontal size (HSIZE), corner correction (HCOR) and trapezium correction (HTRAP), as well as analogue input horizontal size modulation (HSMOD). HTRAP can be set/reset by control bit VPC and HCOR by control bit VSC. HPIN, HCOR and HTRAP track with both vertical and horizontal size (VSIZE/HSIZE), vertical position (VPOS) and analogue modulation input HSMOD.

Two modes of EWDRV operation can be chosen via control bit FHMULT:

- 1. FMULT=1: the EWDRV wave-form tracks with horizontal frequency, used for driving EW diode modulator stages which require a voltage, proportional to line frequency.

- 2. FMULT=0: EWDRV wave-form does not track with horizontal frequency, used for EW modulators that need a voltage, independent on line frequency (e.g. B+ converter circuits).

Figure 8.2 to Figure 8.5 show the effect of register values on the EWDRV voltage wave-form.

# Application Note AN97072

### 8.3 Application

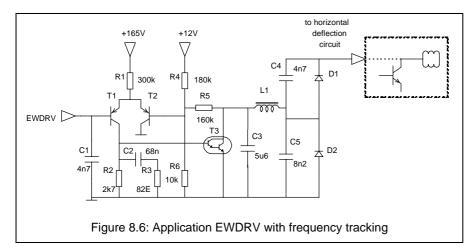

EWDRV can be used in two modes:

1. With line frequency tracking: FMULT=1, EWDRV is used to feed the amplifier that controls the amplitude

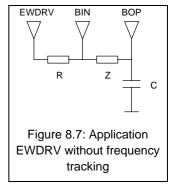

- Without line frequency tracking: FMULT=0, this is used in separate EHT/deflection systems. In this case, the application consists of a resistor to BIN (pin 5), see Figure 8.7. The value for resistor R is typically 56kΩ. For other applications, see Application Notes:

- 'B+ Topologies for Horizontal Deflection and EHT with TDA4855/58', AN96052, see ref. 6.

- 'Circuit Description of CCM420 Monitor', AN97032, see ref. 7.

of horizontal deflection. This option is used in combined EHT/deflection applications that use the diode modulator. The application is shown in Figure 8.6. This is also described in Application Note 'Modification of 15" Autosync Monitor MK-II to Positive Feedback-Pulse Concept', ETV/AN96002 (see ref. 1), which is an update of Application Note AN95086 (see ref. 2).

# 9. PIN 12 / 13: VOUT2 / VOUT1

# 9.1 Characteristics / Internal configuration

| SYMBOL                                            | CONDITIONS                                        | MIN.  | TYP.  | MAX.  | UNIT |                      |

|---------------------------------------------------|---------------------------------------------------|-------|-------|-------|------|----------------------|

| $\Delta I_{VOUT} =$                               | Nominal vertical settings:                        | 0.76  | 0.85  | 0.94  | mA   |                      |

| I <sub>vout1</sub> - I <sub>vout2</sub>           | VSIZE=127 <sub>DEC</sub> and VOVSCN=0, VSMOD=0µA, |       |       |       |      |                      |

| (peak-peak value)                                 | VPC=1, VSC=1, VLC=1, HPC=1.                       |       |       |       |      |                      |

| I <sub>vout1(max)</sub> , I <sub>vout2(max)</sub> | Control bit VOVSCN=1                              | 0.54  | 0.6   | 0.66  | mA   |                      |

| V <sub>vout1</sub> , V <sub>vout2</sub>           | allowed voltage                                   | 0     | -     | 4.2   | V    |                      |

| $\delta V_{\text{offset}}$                        | Nominal vertical settings                         | -     | -     | ±2.5  | %    | 12 🗖                 |

| $\delta V_{\text{linearity}}$                     | Nominal vertical settings                         | -     | -     | ±1.5  | %    | Figure 9.1: Vertical |

| vertical size                                     | Nominal vertical settings;                        | -     | 60    | -     | %    | current outputs      |

|                                                   | register VSIZE = $0_{DEC}$ , bit VOVSC = 0.       |       |       |       |      |                      |

|                                                   | Nominal vertical settings;                        | -     | 100   | -     | %    |                      |

|                                                   | register VSIZE = $127_{DEC}$ , bit VOVSC = 0.     |       |       |       |      |                      |

| vertical size                                     | Nominal vertical settings;                        | -     | 70    | -     | %    |                      |

|                                                   | register VSIZE = $0_{DEC}$ , bit VOVSC = 1.       |       |       |       |      |                      |

|                                                   | Nominal vertical settings;                        | 115.9 | 116.8 | 117.7 | %    |                      |

|                                                   | register VSIZE = $127_{DEC}$ , bit VOVSC = 1.     |       |       |       |      |                      |

| vertical size                                     | $I_{VSMOD} = 0 \ \mu A$                           | -     | 100   | -     | %    |                      |

|                                                   | $I_{VSMOD} = -120 \ \mu A$                        | -     | 93    | -     | %    |                      |

| vertical shift,                                   | register VPOS = $0_{DEC}$ , bit VPC = 0           | -     | -11.5 | -     | %    |                      |

| referred to vertical size of 100%                 |                                                   |       |       |       |      |                      |

|                                                   | register VPOS = $127_{DEC}$ , bit VPC = 0         | -     | 11.5  | -     | %    |                      |

|                                                   | register VPOS = $X_{DEC}$ , bit VPC = 1           | -     | 0     | -     | %    |                      |

25

### 9.2 Description

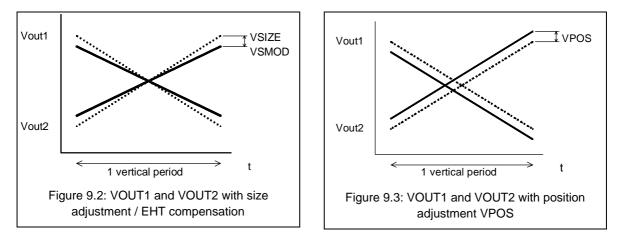

The vertical outputs VOUT1 and VOUT2 are differential current outputs, superimposed on a common bias current source of 300  $\mu$ A. The amplitude can be adjusted by register VSIZE and modulation input VSMOD for EHT compensation, see Figure 9.2. For the VGA350 mode, the register VOVSCN can activate an increase of 17% in vertical size.

Vertical position is adjusted via register VPOS, depicted in Figure 9.3. The vertical size and position also affect the EWDRV output, focus parabola, vertical linearity and vertical linearity balance. In this way, re-adjustment of these parameters is not necessary after altering vertical size or position.

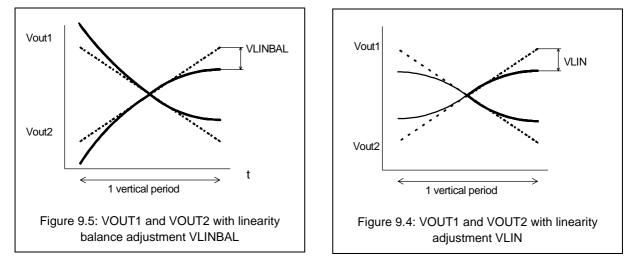

Vertical linearity is adjustable by register VLIN (see Figure 9.4) and can be switched off by control bit VSC. The same holds for vertical S-correction unbalance, adjusted by register VLINBAL (see Figure 9.5) and switched on/off by control bit VLC.

# Application Note AN97072

### 9.3 Application

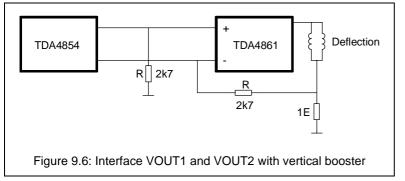

The differential output currents VOUT1 and VOUT2 can be directly coupled to the vertical deflection boosters with differential current inputs, such as TDA8354 or TDA4866. Other boosters which have the traditional op-amp configuration (e.g. TDA4861) need an interface as shown in Figure 9.6.

### 9.4 Lay-out

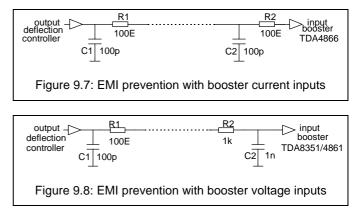

PCB tracks should be as short as possible. The loop area, formed by tracks from VOUT1, VOUT2, BOOSTER\_IN1 and BOOSTER\_IN2, should be as small as possible. This means that the tracks from VOUT1 to BOOSTER\_IN1 and VOUT2 to BOOSTER\_IN2 should be as close as possible to one another. If tracks longer than approximately 10 cm are used, both outputs of the TDA4853/54 as well as inputs of the booster should be filtered for EMI prevention. This is shown in Figure 9.7 for a booster with current inputs and in Figure 9.8 for a booster with voltage inputs. C1 and C2 should be as close to the IC's pins as possible.

#### 10. PIN 14: VSYNC

### **10.1** Characteristics / Internal configuration

| SYMBOL                   | CONDITIONS                   | MIN. | TYP. | MAX. | UNIT |

|--------------------------|------------------------------|------|------|------|------|

| V <sub>VSYNC</sub>       | input signal                 | 1.7  | -    | -    | V    |

|                          | slicing level                | 1.2  | 1.4  | 1.6  | V    |

| IVSYNC                   | 0 < V <sub>SYNC</sub> < 5.5V | -    | -    | ±10  | mA   |

| t <sub>VSYNC(max)</sub>  |                              | -    | -    | 400  | μs   |

| t <sub>delay(VPOL)</sub> | polarity change              | 0.45 | -    | 1.8  | ms   |

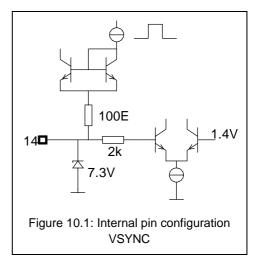

### 10.2 Description

Vertical synchronisation input (VSYNC) slices TTL signals at 1.4V. The output of the vertical sync slicer goes into a polarity normaliser. Then it is OR-ed with the vertical sync pulses generated by the vertical integrator which extracts vertical sync from composite sync applied on pin 15, H/C-sync. The output of this OR-function is fed to the vertical oscillator.

#### 10.3 Application

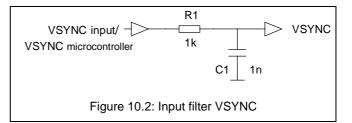

VSYNC is connected directly to the vertical sync input or to the vertical sync output of the microcontroller via a series resistor. Tracks should be kept as short as possible. If tracks are longer than approximately 10 cm, an input filter should be implemented, as shown in Figure 10.2.

### 11. PIN 15: HSYNC

### 11.1 Characteristics / Internal configuration

| SYMBOL                                               | CONDITIONS                                    | MIN. | TYP. | MAX. | UNIT |                                        |

|------------------------------------------------------|-----------------------------------------------|------|------|------|------|----------------------------------------|

| t <sub>HSYNC(max)</sub> \<br>T <sub>horizontal</sub> |                                               | -    | -    | 25   | %    |                                        |

| t <sub>delay(HPOL)</sub>                             |                                               | 0.3  | -    | 1.8  | ms   |                                        |

| DC-coupled TTL signals                               |                                               |      |      |      |      |                                        |

| V <sub>HSYNC</sub>                                   | input signal                                  | 1.7  | -    | -    | V    |                                        |

|                                                      | slicing level                                 | 1.2  | 1.4  | 1.6  | V    |                                        |

| I <sub>HSYNC</sub>                                   | V <sub>HSYNC</sub> = 0.8V                     | -    | -    | -200 | μΑ   | Figure 11.1: Internal pin configuratio |

|                                                      | V <sub>HSYNC</sub> = 5.5V                     | -    | -    | 10   | μΑ   | 1∟                                     |

| t <sub>W_HSYNC(min)</sub>                            |                                               | 0.7  | -    | -    | μs   | 1                                      |

| t <sub>rise_HSYNC</sub>                              |                                               | 10   | -    | 500  | ns   | 1                                      |

| $t_{fall\_HSYNC}$                                    |                                               | 10   | -    | 500  | ns   | 1                                      |

| AC-coupled v                                         | ideo signals                                  | •    | •    |      | •    | 1                                      |

| V <sub>HSYNC</sub>                                   | input signal                                  | -    | 300  | -    | mV   | 1                                      |

|                                                      | slicing level (50 $\Omega$ source)            | 90   | 120  | 150  | mV   | 1                                      |

| $V_{clamp\_HSYNC}$                                   | top sync clamping level                       | 1.1  | 1.28 | 1.5  | V    | 1                                      |

| I charge_HSYNC                                       | V <sub>HSYNC</sub> > V <sub>clamp_HSYNC</sub> | 1.7  | 2.4  | 3.4  | μΑ   | 1                                      |

| $t_{W\_HSYNC(min)}$                                  |                                               | 0.7  | -    | -    | μs   | 1                                      |

| R <sub>source(max)</sub>                             | duty cycle = 7%                               | -    | -    | 1500 | Ω    | 1                                      |

| r                                                    | during sync                                   | -    | 80   | -    | Ω    | 1                                      |

### 11.2 Description

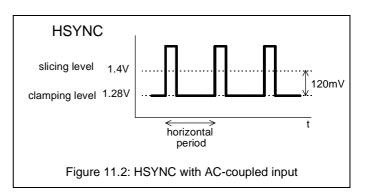

Horizontal sync input (HSYNC) can handle both DCcoupled TTL signals (horizontal or composite sync) and AC-coupled negative-going video sync signals. DC-coupled TTL signals are sliced at 1.4 V and have a limited input current. AC-coupled syncs are clamped to 1.28 V and sliced at 1.4 V, resulting in a fixed absolute slicing level of 120mV, see Figure 11.2. For both input signals, the separated sync signal is integrated and polarity is normalised. Normalised horizontal sync pulses are fed to the

# Application Note AN97072

vertical sync integrator, PLL1 phase detector and frequency locked loop. Equalisation pulses are prohibited for correct functioning of the PLL1 phase detector.

### 11.3 Application

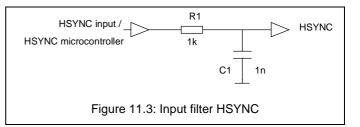

HSYNC is connected directly to the horizontal sync input, to the horizontal sync output of the microcontroller via a series resistor or to the green colour channel for a Sync-On-Green (SOG) application. Tracks should be kept as short as possible. If tracks are longer than approximately 10 cm, an input filter should be implemented, as shown in Figure 11.3.

### 12. PIN 16: CLBL

### 12.1 Characteristics / Internal configuration

| SYMBOL                                       | CONDITIONS                     | MIN. | TYP. | MAX. | UNIT |

|----------------------------------------------|--------------------------------|------|------|------|------|

| V <sub>clamp</sub>                           | top level                      | 4.32 | 4.75 | 5.23 | V    |

| t <sub>clamp</sub>                           | V <sub>CLBL</sub> = 3 V        | 0.6  | 0.7  | 0.8  | μs   |

| slope clamp pulse                            | $R_L = 1 M\Omega; C_L = 20 pF$ | -    | 50   | -    | ns∖V |

| t <sub>delay_clamp</sub>                     | trailing edge horizontal sync; | -    | 130  | -    | ns   |

|                                              | control bit CLAMP = 0;         |      |      |      |      |

|                                              | V <sub>CLBL</sub> = 3 V.       |      |      |      |      |

| t <sub>clamp(max)</sub>                      | trailing edge horizontal sync; | -    | -    | 1.0  | μs   |

|                                              | control bit CLAMP = 0;         |      |      |      |      |

|                                              | V <sub>CLBL</sub> = 3 V.       |      |      |      |      |

| t <sub>clamp(max)</sub>                      | leading edge horizontal sync;  | -    | -    | 0.15 | μs   |

|                                              | control bit CLAMP = 1;         |      |      |      |      |

|                                              | V <sub>CLBL</sub> = 3 V.       |      |      |      |      |

| t <sub>delay_clamp</sub>                     | leading edge horizontal sync;  | -    | 300  | -    | ns   |

|                                              | control bit CLAMP = 1;         |      |      |      |      |

|                                              | V <sub>CLBL</sub> = 3 V.       |      |      |      |      |

| V <sub>CLBL_blank</sub>                      | top level                      | 1.7  | 1.9  | 2.1  | V    |

| t <sub>CLBL blank</sub> (also at<br>HUNLOCK) | control bit VBLK = 0           | 220  | 260  | 300  | μs   |

| t <sub>CLBL blank</sub> (also at<br>HUNLOCK) | control bit VBLK = 1           | 300  | 340  | 380  | μs   |

| V <sub>CLBL_vscan</sub>                      | I <sub>CLBL</sub> = 0          | 0.59 | 0.63 | 0.67 | V    |

| I <sub>CLBL_sink</sub>                       |                                | 2.4  | -    | -    | mA   |

| CLBL_source                                  |                                | -    | -    | -3.0 | mA   |

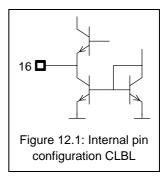

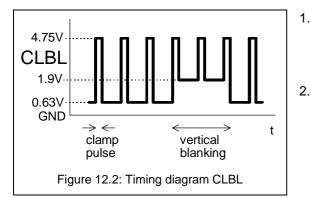

### 12.2 Description

The video clamping/vertical blanking signal CLBL is a sand-castle pulse which is especially suitable for video controllers, such as the TDA488x-family, but also for direct application to video output stages. The signal consists of two levels (see Figure 12.2):

# Application Note AN97072

- The upper level (4.75 V) is video clamping, triggered by the trailing or leading edge of the horizontal sync pulse ( $I^2C$ -selectable by control bit CLAMP). Pulse width is determined by an internal monoflop.

- . The lower level (1.9 V) is vertical blanking, derived directly from the internal oscillator wave-form.

Continuous blanking will be activated if one of the following conditions is true:

- 1. Soft start of horizontal and B+ drive (HPLL2 (pin 30) pulled down, externally or via l<sup>2</sup>C-bus);

- 2. Frequency-locked loop is in search mode (PLL1 unlocked);

- 3. No horizontal flyback pulses at HFLB (pin 1);

- 4. X-ray protection is activated;

- 5. Supply voltage  $V_{cc}$  (pin 10) is below 3.5 V.

Horizontal unlock blanking can be switched off via control bit BLKDIS while vertical blanking and protection blanking remain.

### 12.3 Application

The CLBL output can be used in two applications:

- Coupled to the clamping/blanking inputs of video controller TDA488x via a series resistor of 100Ω. These

video controllers can extract the vertical blanking with negligible delay. However, if (additional) vertical

blanking on grid 1 is wanted, the CLBL is less suitable because of the delay that is caused by filtering out

the 4.75V clamping pulses. In this case it is recommended to use the HUNLOCK signal (pin 17).

- 2. Directly to the output amplifier for black level stabilisation.

### 13. PIN 17: HUNLOCK

### 13.1 Characteristics / Internal configuration

| SYMBOL                                          | CONDITIONS                                                                 | MIN. | TYP. | MAX. | UNIT |

|-------------------------------------------------|----------------------------------------------------------------------------|------|------|------|------|

| V <sub>HUNLOCK</sub>                            | internal sink current = 1 mA                                               | -    | -    | 250  | mV   |

| low level                                       | saturation voltage with locked PLL1                                        |      |      |      |      |

| V <sub>HUNLOCK,BLANK</sub><br>vertical blanking | internal sink current = 2 mA                                               | 0.9  | 1    | 1.1  | V    |

| I <sub>HUNLOCK</sub><br>sink/source current     | V <sub>HUNLOCK</sub> = 1 V                                                 | -    | -    | ±2   | mA   |

| I <sub>HUNLOCK,LEAK</sub>                       | V <sub>HUNLOCK</sub> = 5 V, with PLL1 unlocked<br>and/or protection active | -    | -    | ±5   | μA   |

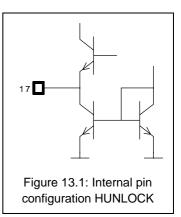

### 13.2 Description

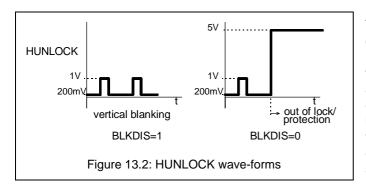

HUNLOCK indicates an out of lock situation of PLL1. This can occur in either search/protection mode or an out of range situation. It can be detected by the microcontroller if an external pull-up resistor is applied to +5V, because HUNLOCK will be floating in case of an out of lock situation. Additionally, HUNLOCK will generate fast vertical blanking signals of 1V. Unlock blanking can be switched off by control bit BLKDIS, while vertical blanking remains. This is necessary for enabling on-screen display in case of missing/wrong sync. HUNLOCK signals are depicted in Figure 13.2.

### 13.3 Application

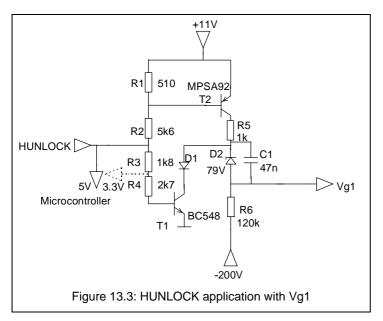

The HUNLOCK pin can be used for three purposes:

- 1. fast vertical blanking at grid1 during normal operation. The 1 V pulse is fed via R3 + R4 and amplified by transistor T1. Note: in this situation transistor T2 is fully conducting.

- 2. protection blanking ; HUNLOCK is floating and pulled up by R2. The output voltage of 5V is determined by the ratio of R2 and R3+R4. In this situation transistor T2 is blocked and consequently Vg1 will drop quickly to -200 Volt, blanking any picture completely.

- 3. Information to the microprocessor. Note: The vertical blanking of 1Volt will not be recognized by an input of the microprocessor. Note: If the microprocessor needs 3.3V on its input, the dashed connection should be used.

Full grid1 blanking will also occur when the 11 Volt supply is lowered. For good spot suppression at power switch off, it is recommended to connect the supply of the circuit in Figure 13.3 to the supply of the vertical output stage, because this 11V disappears quicker than the supply voltage of the TDA4853/54.

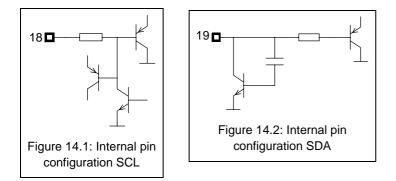

#### 14. PIN 18 / 19: SCL / SDA

#### 14.1 Internal configuration

#### 14.2 Description

The characteristics and application of I<sup>2</sup>C-bus clock input (SCL) and data input (SDA) are described in detail in the Philips data handbook IC12: 'I<sup>2</sup>C Peripherals' (see ref. 3).

### 14.3 Application

The  $I^2C$  inputs are connected via a series resistor to the SDA/SCL lines of the master. If the  $I^2C$ -bus is controlled by a PC, software and an interface-board are necessary. This software and interface are described in Laboratory Report ETV8835: 'User's Guide to  $I^2C$ -bus Control Programs' (see ref. 4).

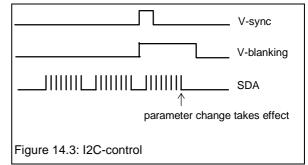

If register contents are changed during the vertical scan, this might result in a visible interference on the screen. The cause for this interference is the abrupt change of picture geometry which takes effect at random locations within the visible picture. To avoid this kind of interference, at least the adjustment of the critical geometry parameters HSIZE, HPOS, VSIZE and VPOS should be synchronized with the vertical flyback. This should be done in such a way, that the adjustment change takes effect during the vertical blanking time. For very slow I2C bus interfaces, it might be neccessary to delay the transmission of the last byte (or only the last bit) of a I2C message until the start of V-sync or V-blanking.

### 15. PIN 20: ASCOR

# 15.1 Characteristics / Internal configuration

| SYMBOL                                     | CONDITIONS                                               | MIN. | TYP.   | MAX. | UNIT            |                        |

|--------------------------------------------|----------------------------------------------------------|------|--------|------|-----------------|------------------------|

| V <sub>ASCOR</sub> maximum<br>output       |                                                          | -    | 6.5    | -    | V               | 480                    |

| V <sub>ASCOR</sub> centre<br>output        |                                                          | -    | 4.0    | -    | V               |                        |

| V <sub>ASCOR.min</sub> minimum<br>output   |                                                          | -    | 1.9    | -    | V               |                        |

| V <sub>ASCOR</sub> maximum<br>output swing |                                                          | -    | 4      | -    | V <sub>pp</sub> | 20                     |

| I <sub>ASCOR</sub> maximum                 |                                                          | -    | -1.5   | -    | mA              | Figure 15.1:           |

| output current                             |                                                          |      | +0.05  |      |                 | Internal pin           |

|                                            | Nominal vertical settings (unless specified otherwise):  |      |        |      |                 | configuration<br>ASCOR |

|                                            | VSIZE=127 <sub>DEC</sub> and VOVSCN=0, VSMOD=0µA, VPC=1, |      |        |      |                 | Addor                  |

| values below                               | VSC=1, VLC=1, HPC=1.                                     |      |        |      |                 |                        |

| $\Delta V_{\text{ascor,hparal}}$           | Register HPARAL=0 <sub>DEC</sub>                         | -    | -0.825 | -    | V <sub>pp</sub> |                        |

| vertical saw-tooth                         | control bit HPC=0                                        |      |        |      |                 |                        |

|                                            | Register HPARAL=15 <sub>DEC</sub>                        | -    | 0.825  | -    | V <sub>pp</sub> |                        |

|                                            | control bit HPC=0                                        |      |        |      |                 |                        |

|                                            | Register HPARAL=X <sub>DEC</sub>                         | -    | 0.05   | -    | V <sub>pp</sub> |                        |

|                                            | control bit HPC=1                                        |      |        |      |                 |                        |

| $\Delta V_{\text{ASCOR},\text{HPINBAL}}$   | Register HPINBAL=0 <sub>DEC</sub>                        | -    | -1.0   | -    | V <sub>pp</sub> |                        |

| vertical parabola                          | Control bit HBC=0                                        |      |        |      |                 |                        |

|                                            | Register HPINBAL=15 <sub>DEC</sub>                       | -    | 1.0    | -    | V <sub>pp</sub> |                        |

|                                            | Control bit HBC=0                                        |      |        |      |                 |                        |

|                                            | Register HPINBAL=X <sub>DEC</sub>                        | -    | 0.05   | -    | V <sub>pp</sub> |                        |

|                                            | Control bit HBC=1                                        |      |        |      |                 |                        |

### 15.2 Description

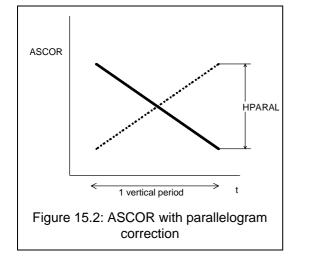

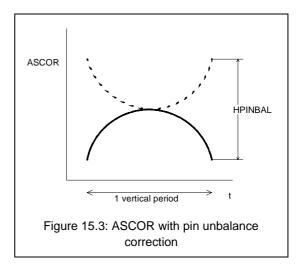

Asymmetric EW-correction (ASCOR) is a voltage output for superimposed wave-forms of vertical parabola and saw-tooth. Amplitude and polarity can be controlled by horizontal parallelogram (register HPARAL) and horizontal pin unbalance (register HPINBAL). Figure 15.2 and Figure 15.3 show ASCOR with adjustment of registers HPARAL for parallelogram correction and HPINBAL for vertical centre-line adjustment.

### Application Note AN97072

Asymmetric correction can be achieved by internal modulation of the PLL2 horizontal phase (control bit ACD=1) or by external DC-shift of horizontal deflection (control bit ACD=0). If a tube is used that does not need asymmetric corrections, ASCOR can also serve other purposes.

### 15.3 Application

Three different applications for ASCOR are possible:

- 1. Control bit ACD=0: asymmetric correction is achieved by feeding ASCOR to the DC-amplifier that controls DC-shift of horizontal deflection by means of a DC-shift transformer.

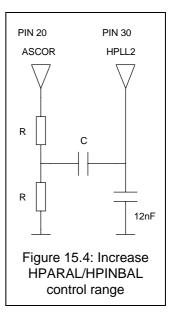

- 2. Control bit ACD=1: asymmetric correction is achieved by internal modulation of PLL2 horizontal phase. ASCOR pin is left unused, because the correction is performed internally. In this case, the control range of HPARAL and HPINBAL can be increased by the application in Figure 15.4. Start values are: R=330kΩ and C=100nF. Increase R for a smaller adjustment range. The soft-start time is increased to about 400 ms with the values mentioned. Note: If bending of the top of the vertical line occurs at maximum HPARAL amplitude, reduce the 12 nF capacitor value until a minimum of 4n7 Farad.

- 3. Control bit ACD=0: asymmetric correction is not used. If the tube does not need parallelogram or pin unbalance correction, ASCOR pin may be used for other applications, e.g. convergence or vertical focus.

#### 16. PIN 21: VSMOD

### 16.1 Characteristics / Internal configuration

| SYMBOL                  | CONDITIONS                 | MIN. | TYP. | MAX. | UNIT |

|-------------------------|----------------------------|------|------|------|------|

| vertical size           | $I_{_{VSMOD}} = 0 \ \mu A$ | -    | 100  | -    | %    |

|                         | $I_{vSMOD}$ = -120 $\mu$ A | -    | 93   | -    | %    |

| V <sub>ref(VSMOD)</sub> |                            | -    | 5.0  | -    | V    |

| R <sub>VSMOD</sub>      |                            | 300  | -    | 500  | Ω    |

| B <sub>VSMOD</sub>      |                            | 1    | -    | -    | MHz  |

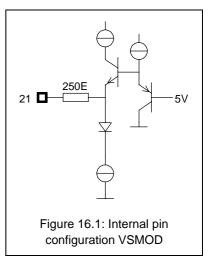

### 16.2 Description

Vertical size modulation (VSMOD) is an analogue modulation input for size compensation with changing EHT. In case of a combined EHT/deflection application, it is used to compensate for load variations. Modulation at this pin will result in a vertical size reduction of 0 - 7%.

**Note**: The polarity of VSMOD (and HSMOD) is inverted, compared to VAMP (and EWWID) of the TDA4855.

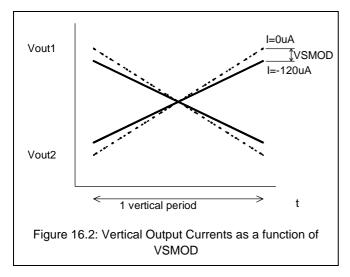

Size reduction is achieved by correcting the differential output currents at VOUT1 and VOUT2. It does not affect EW wave-forms, vertical focus, pin unbalance or parallelogram corrections. Figure 16.2 shows the vertical current outputs as a function of modulation at VSMOD in case of a full white picture on screen.

### 16.3 Application

If the load of an unstabilized EHT increases, the EHT voltage will decrease and thus, vertical size will increase. This increased size can be compensated for by sinking current from VSMOD. Variation in current at VSMOD from 0 to  $-120\mu$ A will result in a vertical size variation of 0 to -7% of the actual size in the differential output currents. Load variations in the EHT can be compensated for via two possible applications:

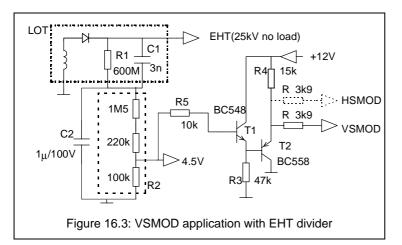

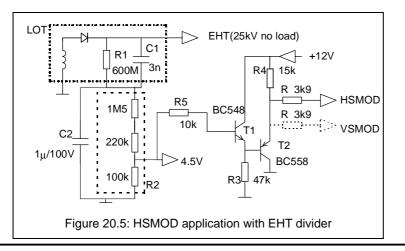

1- A parallel capacitor and bleeder are present in the EHT transformer. With a divider and buffer, EHT information can be transferred to VSMOD. This is the best solution, because the signal does not lag in phase. The application at VSMOD can be implemented as shown in Figure 16.3.

This divider creates a T1 base voltage of 4.8 V, within the range of the voltage at HSMOD. A decrease of EHT voltage will result in a voltage over R, sinking current from HSMOD. The time constants of the divider (C1\*R1 and C2\*R2) should be equal. The values for R2 and C2 should be recalculated if the LOT contains other component values for R1 or C1. C2 should have a low leakage current (< 0.1  $\mu$ A). For a full VSMOD control range with a EHT voltage drop of 10% (2.5kV), the value for R will be 3k9.

For an optimised dimensioning of R, follow the next steps:

- Adjust HSMOD application values;

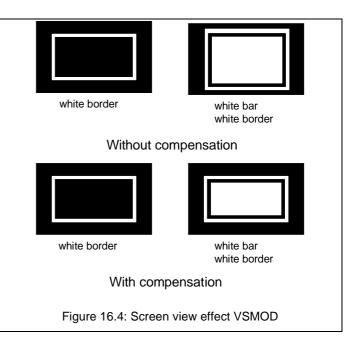

- Display a white bar (about 80% width and 80% height), flashing on/off at about 1Hz, and a white border line for reference (see Figure 16.4);

- Adjust R to an optimised vertical size correction (no displacement in border line on screen) and apply this value as a fixed resistor.

### Application Note AN97072

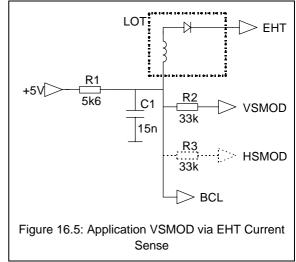

2: The footpoint of the EHT transformer (not grounded) can be used for EHT information via a resistor. This solution will, however, result in a VSMOD phase lag and therefor, geometry compensation will not be optimal. The application of VSMOD in this case is depicted in Figure 16.5.

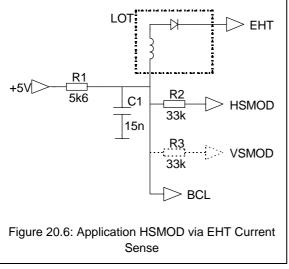

the voltage of HSMOD. A variation in beam current from 0 to 700 $\mu$ A will result in a voltage drop over R1 of 700 $\mu$ \*5k6 = 4V. Now, the value for R2 can be calculated, because an equal voltage drop over R2 should sink 120 $\mu$ A from HSMOD: R2 = 4\120 $\mu$  = 33k $\Omega$ . The time constant  $\tau_1$ , created by R1\* C1, should be between horizontal and vertical period ( $\tau_1 \approx 0.5$  ms).

For an optimised dimensioning of R2, follow the next steps:

- Adjust HSMOD application values;

- Display a white bar (about 80% width and 80% height), flashing on/off at about 1 Hz, and a white border line for reference (see Figure 16.4);

- Adjust R2 to an optimised vertical size correction (no displacement in border line on screen) and apply this value as a fixed resistor.

A slight interaction from VSMOD to HSMOD and vice versa is possible. This VSMOD/HSMOD application concept can also be used for beam current limiting (BCL).

#### 16.4 Lay-out

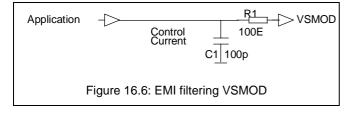

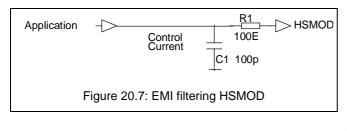

In both applications, tracks should be as short as possible, especially the track from resistor to VSMOD. This resistor is 'R' in Figure 16.3 and R2 in Figure 16.5. If these tracks are longer then approximately 2 cm, input filtering will be necessary in order to eliminate possible EMI problems. This is done by an input filter, shown in Figure 16.6, where R1 and C1 should be as close as possible to the input pin.

17.2

Description

### Bus-Controlled Autosync Deflection Controller TDA4853/54

Figure 17.2: Internal pin configuration VREF

### 17. PIN 22 / 23 / 24: VAGC / VREF / VCAP

### 17.1 Characteristics / Internal configuration

| SYMBOL                                       | CONDITIONS                  | MIN. | TYP. | MAX. | UNIT |                                             |

|----------------------------------------------|-----------------------------|------|------|------|------|---------------------------------------------|

| f <sub>V, free-running</sub>                 | $R_{VREF} = 22 \ k\Omega$   | 40   | 42   | 43.3 | Hz   |                                             |

|                                              | $C_{VCAP} = 100 \text{ nF}$ |      |      |      |      |                                             |

| $\mathbf{f}_{V, \text{ catching range}}$     | $R_{VREF} = 22 \ k\Omega$   | 50   | -    | 160  | Hz   |                                             |

| t <sub>scan delay</sub>                      | control bit VBLK = 0        | 220  | 260  | 300  | μs   |                                             |

| between trigger pulse<br>and start VCAP ramp |                             |      |      |      |      | Ч<br>—                                      |

| t <sub>scan delay</sub>                      | control bit VBLK = 1        | 300  | 340  | 380  | μs   | Figure 17.1: Internal pin configuration VAG |

|                                              |                             |      |      |      |      |                                             |

| V <sub>VREF</sub>                            |                             | -    | 3.0  | -    | V    |                                             |

| C <sub>VAGC</sub>                            |                             | 150  | -    | 220  | nF   |                                             |

| IVAGC                                        | control bit AGDIS = 0       | 120  | 200  | 300  | μA   |                                             |

|                                              | control bit AGDIS = 1       | -    | 0    | -    | μA   |                                             |

|                                              | 24 🗖                        |      |      |      | -    |                                             |

# 24 D Figure 17.3: Internal pin configuration VCAP

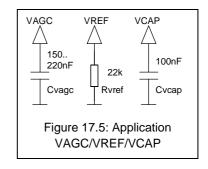

Vertical automatic gain control is done at VAGC, which can be disabled by resetting control bit AGCDIS. The vertical reference input VREF determines the vertical free-running frequency by connecting a resistor to ground, together with capacitor  $C_{VCAP}$  at VCAP.

### Application Note AN97072

### 17.3 Application

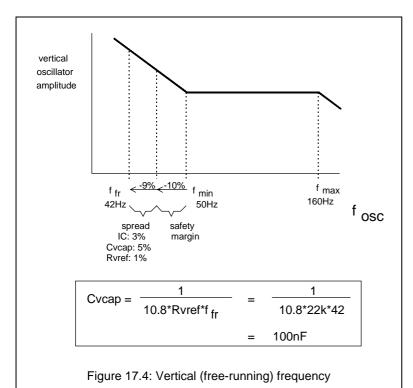

The capacitor  $C_{VCAP}$  connected to vertical capacitor VCAP input determines the freerunning vertical frequency, together with resistor  $R_{VREF}$  (22 k $\Omega$ ) at VREF. Figure 17.4 shows how to determine the value for  $C_{VCAP}$ .

**Note:** For stable internal references as well as optimised noise and linearity performance, always apply a value of  $22k\Omega$  at VREF.

The application of vertical automatic gain control VAGC consists of a capacitor with a value of 150 nF to 220 nF to ground. VAGC should not be loaded externally in order to avoid non-linearities in vertical size. Application of VAGC, VREF and VCAP is shown in Figure 17.5.

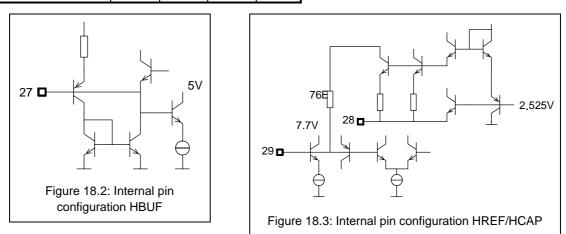

### 18. PIN 26 / 27 / 28 / 29: HPLL1 / HBUF / HREF / HCAP

### 18.1 Characteristics / Internal configuration

| SYMBOL                    | CONDITIONS                | MIN.  | TYP.  | MAX.  | UNIT |

|---------------------------|---------------------------|-------|-------|-------|------|

| t <sub>HPLL1,lock</sub>   |                           | -     | 40    | 80    | ms   |

| I <sub>HPLL1</sub>        | level 1 locked mode       | -     | 15    | -     | μΑ   |

|                           | level 2 locked mode       | -     | 145   | -     | μΑ   |

| V <sub>HBUF</sub>         | f <sub>H(min)</sub>       | -     | 2.5   | -     | V    |

|                           | f <sub>H(max)</sub>       | -     | 0.5   | -     | V    |

| V <sub>HREF</sub>         |                           | 2.43  | 2.55  | 2.68  | V    |

| f <sub>free-running</sub> | R <sub>HBUF</sub> = ∞;    | 30.53 | 31.45 | 32.39 | kHz  |

| for testing               | $R_{HREF} = 2.4k\Omega;$  |       |       |       |      |

| only                      | C <sub>HCAP</sub> = 10nF. |       |       |       |      |

| f <sub>H(max)</sub>       |                           | -     | -     | 130   | kHz  |

#### 18.2 Description

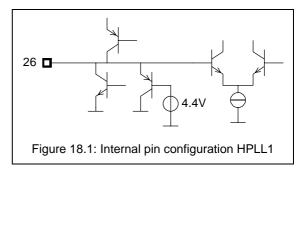

HPLL1 is the loop filter input of the horizontal phase locked loop PLL1, that synchronises the horizontal oscillator with HSYNC. If the oscillator frequency deviates more than 4% of HSYNC, PLL1 goes into search mode. After tuning the horizontal oscillator, PLL1 goes into soft-lock mode during 1/3 of a vertical period and then passes into normal PLL operation.

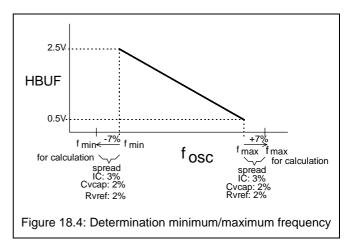

### Application Note AN97072

The minimum horizontal frequency is determined by the capacitor at HCAP and resistor at HREF. Because the capacitor value is fixed (10 nF), the minimum frequency is actually determined by resistor  $R_{HREF}$  only. Horizontal frequency range is determined by resistor  $R_{HBUF}$  from HBUF to HREF. Figure 18.4 shows how to determine minimum and maximum frequency for calculating  $R_{HREF}$  and  $R_{HBUF}$ . TV-mode is centred around  $f_{min}$  (pin HBUF is floating) with a control range of ±10%. This mode is only allowed between 15.625 and 35 kHz.

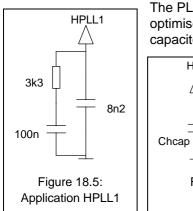

### 18.3 Application

The PLL1 loop filter is connected to HPLL1 (see Figure 18.5). These values are optimised for low jitter. The scan time for search mode is determined by the 100nF capacitor. It is not allowed to load HPLL1 externally. The application of

HBUF/HREF/HCAP is shown in Figure 18.6.

The equations below show how to calculate  $\mathsf{R}_{_{HBUF}}$  and  $\mathsf{R}_{_{HREF}}$ .

HCAP

10nF

HREF

Figure 18.6: Application

HREF/HBUF/HCAP

Rhbuf

Rhref

$$R_{HREF} = \frac{78 * kHz * k\Omega}{f_{min} + 0.0012 * f_{min}^{2} [kHz]}$$

$$R_{HBUF} = \frac{R_{HREF} * \frac{78 * \text{kHz} * \text{k}\Omega}{f_{max} + 0.0012 * f_{max}^{2} [\text{kHz}]}}{R_{HREF} - \frac{78 * \text{kHz} * \text{k}\Omega}{f_{max} + 0.0012 * f_{max}^{2} [\text{kHz}]}} * 0.8$$

Some common values for maximum/minimum frequencies and corresponding values for  $\rm R_{HBUF}$  and  $\rm R_{HREF}$  are shown in the table at the right.

| R <sub>href</sub><br>[Ω] | f <sub>min</sub><br>[kHz] | R <sub>ΗΒυΓ</sub><br>[Ω] | f <sub>max</sub><br>[kHz] |

|--------------------------|---------------------------|--------------------------|---------------------------|

| 5k28                     | 15.625                    | 1k26                     | 56                        |

|                          |                           | 900                      | 72                        |

|                          |                           | 673                      | 90                        |

| 3k4                      | 24                        | 1k51                     | 56                        |

|                          |                           | 1k02                     | 72                        |

|                          |                           | 738                      | 90                        |

| 2k56                     | 31.45                     | 1k85                     | 56                        |

|                          |                           | 1k16                     | 72                        |

|                          |                           | 811                      | 90                        |

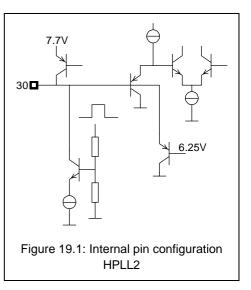

#### 19. PIN 30: PLL2

### **19.1** Characteristics / Internal configuration

| SYMBOL                                                                              | CONDITIONS                                                                                     | MIN. | TYP. | MAX. | UNIT |

|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|------|------|------|------|

| <pre> \$ \$ \$ \$ \$ \$ \$ \$ \$ \$ \$ \$ \$ \$ \$ \$ \$ \$ \$</pre>                | maximum advance;<br>register HPINBAL=07 <sub>DEC</sub> ;<br>register HPARAL=07 <sub>DEC.</sub> | 36   | -    | -    | %    |

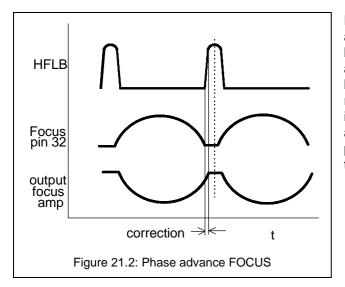

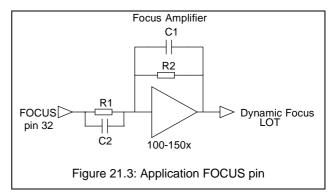

|                                                                                     | minimum advance; register<br>HPINBAL=07 <sub>DEC</sub> ; register<br>HPARAL=07 <sub>DEC.</sub> | -    | 7    | -    | %    |